مبدل تماثلي رقمي

هذه المقالة بحاجة لمراجعة خبير مختص في مجالها. (فبراير_2010) |

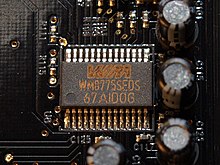

المبدل التماثلي الرقمي أو المحول التناظري الرقمي (بالإنجليزية: Analog-to-digital converter)، اختصاراً ADC، هو وحدة إلكترونية تقوم بتحويل الإشارات الكهربية التماثلية إلى رقمية، حيث يكون هذا الخرج الرقمي ثنائي القيمة (قيمة عليا ويمثل بالرقم 1 وقيمة صغرى ويمثل بالرقم 0).[1][2][3]

أساسيات التشغيل عدل

العينة عدل

Sampling وهي تقسيم الإشارة إلى أجزاء تفصل بينها مدة زمنية قدرها بواسطة مفتاح تلقائي Switch، ويكون تردد هذا المفتاح أكبر من ضعف أكبر تردد في الإشارة المراد تحويلها. ويسمى هذا الزمن بزمن العينة Sampling Time.

الترميز عدل

Quantization تقييم كل مستوى من هذه العينات المأخوذة وإعطاءها قيمة رقمية في عدد من الخانات (Bits) يتم تحديد هذا العدد من البتات بناء على أقصى مستوى تصل إليه الإشارة وكذلك دقة التحويل.

الدقة عدل

تزداد الدقة كلما زاد عدد البتات (N) للمسجل (Register) الموجود داخل المحول ADC حسب:

error=(+/-)(1/2)FSR/2^N

FSR :يمثل المدى الكلي لقيمة الإشارة (Amplitude) لكن (P-P). مثلا (sine wave) تمتلك أعلى قيمة بالموجب 4 وبالسالب -4

لذلك:FSR=8

وكذلك تزداد الدقة بتقليل Ts وهو الزمن بين عينتين (two samples) أي كلما زاد تردد التقسيم (sampling fs)

أنواع المبدلات التماثلية – الرقمية (ADC) عدل

يوجد نوعان من المبدلات التماثلية الرقمية: 1:يستخدم مبدل رقمي تماثلي (DAC) في تغذيته الخلفية وله ثلاث أنواع: (عدادي - متلاحق - تقريب متتالي).

2: لا يستخدم مبدل رقمي تماثلي (DAC) في تغذيته الخلفية وله نوعان: (Flash ADC - مبدل جهد إلى تردد ).

المبدل العدادي عدل

هذا المبدل هو عبارة عن مبدل يستخدم المبدل الرقمي التماثلي (DAC) في تغذيته الخلفية كما يحتوي على عداد تصاعدي حيث أن حجم العداد بنفس حجم المبدل الرقمي التماثلي (DAC) و هذا مخطط له:

يعمل العداد ما دام جهد الدخل Vin أصغر من جهد الخرج لمبدل رقمي تماثلي (DAC) وبالتالي يستمر في العد، وعندما يصبح أكبر من قيمة خرج المبدل الرقمي التماثلي (DAC) يكون خرج المقارن 0 فيبقى الخرج الرقمي ثابت. أحد سلبيات هذا النوع هو وجود عداد في بنيته مما يؤدي إلى وجود زمن تبديل طويل نسبيا، حيث أن العداد تصاعدي فعند قيم معينة يجب التصفير.

ويكون زمن التبديل الأعظم:

حيث هي عدد البتات (bits) و هي زمن تبديل المبدل الرقمي التماثلي (DAC)

المبدل المتلاحق عدل

هو مبدل يحتوي على مبدل رقمي تماثلي (DAC) في تغذيته الخلفية كما يحتوي أيضا على عداد تصاعدي-تنازلي، ولا يعود هذا العداد للصفر أبدا والمخطط التالي يوضح هذا المبدل:

أحد سلبياته أنه لا يستطيع العمل عند حدوث تغيرات سريعة في الإشارة لأنه سيحتاج إلى زمن تبديل أطول، ويصبح غير فعال عندما تكون الإشارات ذات تغيرات سريعة. وبالتالي هو فعال عند الإشارات ذات التغيرات البطيئة.

مبدل التقريب المتتالي التسلسلي (serial successive approximation converter) عدل

(دراسة ل 3bit)

يقوم بعملية مقارنة ما بين Vin و V ref/2 فتكون النتيجة إما:

- فوق، أي الخانة MSB تقابل 1

- أو تحت، أي الخانة MSB تقابل 0

ومن ثم تتم المقارنة من جديد ولكن بالنسبة للمراتب التالية وصولاً إلى تحديد الـ LSB

والشكل يوضح هذه العملية:

هنا في المقارنة الأولى نقارن الدخل مع Vref/ 2 فإذا كان أكبر يكون أول Bit هو 1 وإذا كان أصغر يكون أول Bit هو 0

وهكذا المقارنة الثانية تحدد البت الثاني وهكذا دواليك حتى الوصول إلى آخر مقارنة وهي التي تحدد. LSB أي إن أول قيمة يبدأ بإيجادها هي MSB ثم يقرر بقية الخانات وصول إلى LSB

الخوارزمية عدل

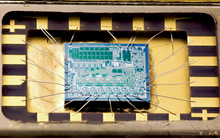

أن تقنية التقريب المتتالي هي التقنية الأكثر استخداما" مع المعالجات المصغرة كطريقة تتصف بالسرعة العالية والكلفة المنخفضة وسنشرح فيما يلي هذه التقنية بالتفصيل حيث أن المبدل ADC المستخدم في المنظومة يستخدم هذه التقنية في التبديل يبين الشكل التالي البنية الداخلية لهذا النوع من المبدلات.

إن مبدأ هذه الطريقة هو توليد قيمة أولية لقيمة الدخل ثم تبديلها إلى قيمة تماثلية وذلك باستخدام مبدل D\A ثم مقارنة هذه القيمة مع القيمة الفعلية وبالاعتماد على نتيجة المقارنة سوف تزداد القيمة الأولية أو تنقص حيث يقوم المتحكم المنطقي بهذه العملية (عملية الزيادة أو النقصان) ويمكن أن نفهم طريقة عمل المبرمج المنطقي بالاعتماد على الشكل التالي الذي يبين المخطط الانسيابي للبرنامج الذي ينفذه المبرمج المنطقي والمرسوم في الصفحة التالية:

المخطط الانسيابي للخوارزمية

إن الخانة التي يكون عليها "1" على مدخل المبدل D\A تؤدي إلى توليد جهد في خرج المبدل قيمته مبينة وفق الجدول التالي

فمثلا جهد الخرج الذي يولده D/A من أجل القيمة 1011 0001 هو:

Vref/2+Vref/8+Vref/16+Vref/256 = (177/256)* Vref وكمثال على سير عملية التقريب المتتالي لنأخذ الشكل التالي الذي يوضح سير عملية التقريب لأجل مبدل بعرض 8 بت.

توضع الخانة الأكثر أهمية MSB بالحالة واحد وتكون القيمة الرقمية على دخل المبدل هي 1000 0000 وبالتالي يوجد على خرج الـ D/A جهداً قيمته V1 = Vref/2 نلاحظ ان قيمته اصغر من قيمة الدخل التماثلي V1 < Vinput لذلك يقوم المتحكم بتثبيت القيمة واحد على الخانة السابعة وينتقل إلى الخانة السادسة فيضع عليها القيمة واحد فتصبح القيمة الرقمية 1100 0000 وبالتالي يتولد جهد قينته V2 = Vref/2 + Vref/4 على خرج الـ D/A ونلاحظ انّ V2 > Vinput لذلك يعود المتحكم المنطقي ويضع القيمة صفرعلى الخانة السادسة وينتقل إلى الخانة الخامسة ويضعها في الحالة واحد أي تصبح القيمة الرقمية 1010 0000 والجهد المقابل لها هو:

V3 = Vref/2 + Vref/8 ونتيجة المقارنة نلاحظ أن V3 < Vinput لذلك يتم تثبيت قيمة الخانة الخامسة بالحالة واحد وينتقل المبرمج ليعالج الخانة الرابعة التالية وهكذا إلى نهاية عملية التقريب.

نلاحظ ان كل خانة تعالج خلال نبضتين اثنتين من نبضات الساعة ولأجل المثال السابق تستغرق عملية التبديل 16 نبضة من نبضات الساعة وبالتالي فإن زمن التبديل ثابت لكل القيم.

تمت المناقشة السابقة على أساس أن الـ Vinput ثابتة خلال عملية التبديل وعلى أساسها حصلنا على زمن تبديل ثابت أما عندما تتغير قيمة الدخل ولمّا ينتهي المتحكم بعد من عملية التبديل فان عملية التبديل ربما تستغرق زمناً أكبر أو تؤدي إلى أخطاء ولحل هذه المشكلة يجب استخدام دارة نمذجة ومسك للعينات Sample and hold لتثبيت قيمة الدخل التي تجري عليها عملية التقريب لفترة زمنية أكبر أو تساوي زمن التبديل Conversion time

ملاحظات عدل

- يمكننا أخذ أي مثال ولكن يجب أن يكون الدخل أصغر من الجهد المرجعي

- إن هذا المبدل هو الأكثر استخداما لأن تميزيته من 8 إلى 16 بت وهي تعتبر تميزية جيدة.

- وهذا المبدل سريع نسبيا لأن عدد حالات المقارنة تساوي عدد خانات المبدل وكلفته ضئيلة.

- Flash ADC.Aِ

تتم المقارنات فيه على شكل تفرعي بدفعة واحدة فيكون عدد المقارنات فيه كبير نطبق جهود على الأقطاب السالبة لمكبر العمليات من جهد مرجعي. الشكل التالي يمثل دارة المبدل:

وإن هذا المبدل يعتمد الجدول التالي للتبديل إلى ترميز معروف

في هذا المبدل نحتاج إلى (2 (n-1)) و يعتبر أسرع المبدلات على الإطلاق تكون المقارنات ذات خرج مساوي لـ 1 في حال كان Vin ما زال أصغر من أجزاء Vref ثم يتم التبديل من ترميز الأغلبية إلى ترميز ثنائي عن طريق كاشف ترميز الأغلبية

- ملاحظة: من الصعب أن نصنع مبدلات ADC تفرعيه بعدد خانات كبير وهي في أحسن الحالات 8Bits

المواصفات الفنية للمبدلات التماثلية – الرقمية عدل

سنستعرض المواصفات الفنية التالية للمبدلات التماثلية الرقمية والرقمية التماثلية: • مجال الدخل والتمييزية. • نوع الترميز. • خطأ التكميم والأخطاء الخطية • الخطأ اللاخطي. • الرموز المفقودة.

1. مجال الدخل والتمييزية (Input voltage range & resolution) عدل

مجال الدخل هو قيم جهود الدخل التي يمكن إنجاز عملية التبديل لها. نقاط نهاية أعلى وأسفل مجال الدخل تسمى أل +Full scale و. -Full scale عندما (0= (–Full Scale يسمى ADC بوحيد القطبية Unipolar وعندما Full scale الأدنى يساوي قيمة سالبة يسمى ADC بثنائي القطبية. Bipolar إذا ازداد جهد الدخل عن المجال المسموح به فالتبديل سيكون خاطئ وال ADC يدخل في حالة تسمى خارج المجال. Over range نعرف التمييزية هو الجهد الأدنى للدخل الذي يكشفه أل ADC ويسمح لخرج المبدل الانتقال من حالة رقمية إلى الحالة المجاورة وهو عادة يساوي (1LSB=VFS/2^n) تقدر عادة التمييزية بعدد الخانات الثنائية للمبدل حيث تعني تمييزية أل 12 bit أن ADC يمكن أن يكشف 2^12 = 4096)) جزء من جهد المجال الكلي VFS.

2. نوع الترميز: (Coding type) عدل

توجد طرائق متعددة لترميز خرج المبدلات التماثلية الرقمية والرقمية التماثلية منها الترميز الثنائي حيث الخانات كلها أصفار عند الجهد صفر فولت وتكون كل الخانات واحدات عند +Full scale ويستخدم هذا الترميز عند الترميز آحادي القطبية Unipolar.

+Full scale V 1111 -Full scale=0 V 0000 النوع الثاني للترميز هو الترميز الثنائي المزاح Offset binary الذي يستخدم إذا كان المبدل ثنائي القطبية أي –Full scale جهد سالب ولكن سيئة هذه الطريقة أن القيمة المكافئة ل 0V لا يكافئ الترميز.00…. 0 +Full scale 1111 1000 0 Volt -Full scale 0000 لجعل القيمة الرقمية 00..0 تتوافق مع القيمة OV نستخدم طريقة الترميز 2’complement كما يلي: نستخدم نفس الترميز الثنائي المزاح مع قلب الخانة MSB في الرمز الرقمي وسنطبق هذه الطريقة على:3-bits ADC

3. خطأ التكميم والأخطاء الخطية (Quantization error & linear errors) عدل

يجب التمييز بين الخطأ الناتج عن عملية التبديل وبسبب محدودية عدد أل Bits في ADC (عادة يسمى هذا الخطأ بخطأ التكميم المتأصل (Inherent quantization error والخطأ الخطي الناتج عن عدم مثالية دارة. ADC

سنبدأ بشرح الخطأ المتأصل في التكميم. بسبب محدودية عدد الرموز في خرج أي مبدل ADC سيكون هناك خطأ تبديل يصل حتى قيمة ±0.5 LSB انظر الشكل (1-35) الذي يبين خطا التكميم المصاحب لعملية التبديل التماثلي الرقمي 3bit ADC مع ترميز آحادي القطبية والشكل (1-36) يبين تابع التبديل 3bits ADC ذو ترميز ثنائي القطبية غير مزاح.

إن خطأ التكميم أو ضجيج التكميم هو خطأ ملازم لعملية التكميم ولا يمكن تجنبه ولكن يمكن تقليله بزيادة عدد خانات bits المبدل التماثلي الرقمي) أي رفع تمييزية المبدل(يعتبر خطأ التكميم إشارة سن منشار ذات قيمة أعظمية ±0.5 LSB والتي تساوي. VFS/ 2 (n+1)

القيمة الفعالة لخطأ التكميم Eqتعطى بالعلاقة: Eq = 0.5 LSB / 3 (0.5)

وبتبديل قيمة 0.5 LSB بدلالة VFS نحصل على العلاقة:

Eq=VFS/2 (N)√12

تعتبر الأخطاء الخطية غير المتأصلة أخطاء ذات قيمة عالية، ومن حسن الحظ يمكن تصحيحها بمعايرة بسيطة أو بإضافة أو بالضرب بمعامل تناسب للتصحيح. الأخطاء الخطية لا تابع التبديل ولكن فقط تغير مجال الدخل الذي يعمل عليه أل.ADC تشوه الخطأ الخطي الغير متأصل نوعين إما خطأ إزاحة Offset Error أو خطأ ربح Gain error. خطأ الإزاحة يجعل الخط المستقيم المار من مراكز عبور رموز الخرج يصعد أو يزاح إلى الأعلى في المثال المبين في الشكل(1-37) مقدار الإزاحة 0.6 LSB لمبدل 3-bits ADC ذو ترميز ثنائي القطبية والشكل الآخر أسفله يبين نتيجة الخطأ.

خطأ الربح يجعل ميل الخط المستقيم(تابع التبديل) المار من مراكز عبور رموز الخرج يتغير من حالته المثالية التي تساوي الواحد إلى قيمة أخرى. في المثال المبين في الشكل (1-38) من الملاحظ تغير الميل من القيمة 1 المثالية ليصبح 1.25 وبالتالي خطأ الربح في مثالنا يساوي 25% لمبدل3 -bits ADC ونلاحظ في الشكل السفلي للشكل(1-38) تغير نتيجة الخطأ على كامل مجال جهد الدخل. يمكن تعويض خطأ الإزاحة بإضافة جهد تصحيح باستخدام دارة مقسم جهد أو بإضافة ثابت إلى الرمز الثنائي، كم يمكننا تعويض خطأ الربح بإضافة مكبر متحكم بالجهد Voltage controlled amplifiers أو بضرب الرمز الثنائي الناتج بثابت

4.الأخطاء اللاخطية: (ADC&DAC nonlinear errors) عدل

المبدلات ADC الحقيقية أو العملية ليست مثالية، والشكل (1-39) يبين تابع تبديل غير مثالي لمبدل 3Bits ADC. يوجد نوعين من الأخطاء اللاخطية التي تستخدم كمواصفات لـ ADC الحقيقية: اللاخطية الديناميكية: The dynamic nonlinearity، المختزلة DNL، هي الفرق الحقيقي لكل خطوة والعرض المثالي لـ LSB.

اللاخطية المتممة: Integral nonlinearity، المختزلة INL، هو الفرق بين الحالة العابرة والخط المستقيم المار خلال قمم الحالات العابرة الأولى والأخيرة. عادة، يعبر عن DNL ،INL بواحدة, LSB كما أن قيمة LSB تعطى بالعلاقة:

من الصعب تعويض الأخطاء اللاخطية بنوعيها لذا نلجأ عادة لتخفيضه للحد الأدنى.

5. الرموز المفقودة: (ADC missing codes) عدل

الأداء الجيد ل ADC أن لا يحتوي في خرجه على رموز Codes مفقودة. هذا يعني عندما نمسح جهد الدخل على كامل المجال فإن كل تراكيب الترميز في الخرج يجب أن تظهر. الشرط اللازم كي نضمن عدم فقدان أي رمز في الخرج، هو فقط إذا كان الخطأ الديناميكي اللاخطي DNL أقل من ±1 LSB. الشكل (1- 40) يبين أن الرمز 10 مفقود من الخرج وذلك عندما نمسح جهد الدخل من 0V حتى. VFS

هذه الوصلة للموقع التي تم منه جمع المعلومات والمرجع الأساسي.

انظر أيضًا عدل

مراجع عدل

- ^ "معلومات عن محول تناظري رقمي على موقع jstor.org". jstor.org. مؤرشف من الأصل في 2019-09-02.

- ^ "معلومات عن محول تناظري رقمي على موقع d-nb.info". d-nb.info. مؤرشف من الأصل في 2019-12-13.

- ^ "معلومات عن محول تناظري رقمي على موقع britannica.com". britannica.com. مؤرشف من الأصل في 2019-09-02.

| في كومنز صور وملفات عن: مبدل تماثلي رقمي |